### AME 3623: Embedded Real-Time Systems: Final Exam

Solution Set May 13, 2005

| Problem | Topic                 | Max | Grade |

|---------|-----------------------|-----|-------|

| 0       | -                     | 2   |       |

| 1       | Logic                 | 70  |       |

| 2       | Arithmetic            | 15  |       |

| 3       | Microprocessor Design | 30  |       |

| 4       | Interrupts and I/O    | 33  |       |

| 5       | Serial Communication  | 30  |       |

| 6       | Finite State Machines | 20  |       |

| 7       | Bonus                 | 2   |       |

| Total   |                       | 202 |       |

# 1. Logic

|   | Б | a | Б |   |

|---|---|---|---|---|

| А | В | С | D | f |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

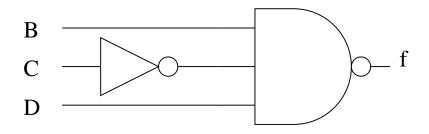

Given the following function:

(a) (10 pts) Show the Karnaugh map and the clusters.

|   |    | ٨D | $\begin{array}{c c} & & & A \\ & & B \\ & 00 & 01 & 11 & 10 \end{array}$ |                   |                | 1 |

|---|----|----|--------------------------------------------------------------------------|-------------------|----------------|---|

|   | CD | AB |                                                                          |                   |                |   |

|   |    | 00 | 1                                                                        | 1<br>(0<br>1<br>1 | 1              | 1 |

|   |    | 01 | 1                                                                        | 0                 | $\overline{0}$ | 1 |

|   | D  | 11 | 1                                                                        | 1                 | 1              | 1 |

| C |    | 10 | 1                                                                        | 1                 | 1              | 1 |

(b) (7 pts) What is the algebraic expression for the corresponding circuit?

$$f = \overline{B\overline{C}D}$$

(c) (7 pts) Show the circuit

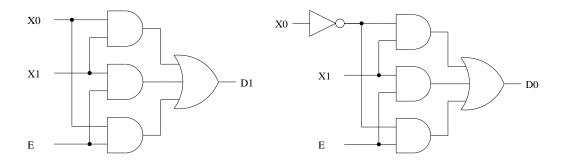

Given the following circuits:

(d) (15 pts) Show the corresponding truth table for D0 and D1.

| E | X1 | X0 | D1 | D0 |

|---|----|----|----|----|

| 0 | 0  | 0  | 0  | 0  |

| 0 | 0  | 1  | 0  | 0  |

| 0 | 1  | 0  | 0  | 1  |

| 0 | 1  | 1  | 1  | 0  |

| 1 | 0  | 0  | 0  | 1  |

| 1 | 0  | 1  | 1  | 0  |

| 1 | 1  | 0  | 1  | 1  |

| 1 | 1  | 1  | 1  | 1  |

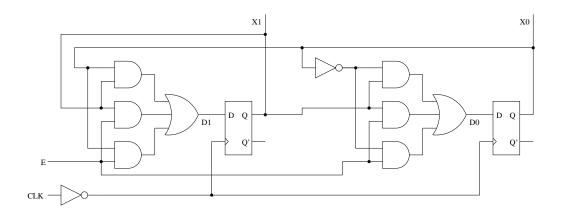

Given the following sequential logic circuit (note its relationship to the circuits in the previous problem):

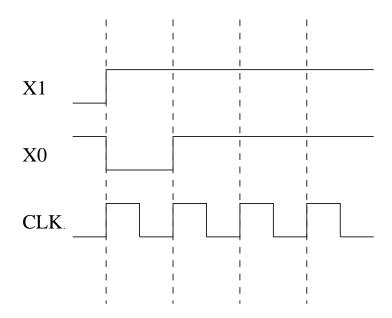

(e) (8 pts) Assume an initial condition of X1 = 0 X0 = 1, and that E = 1. Show the timing diagram for 4 clock cycles (include X1, X0 and CLK).

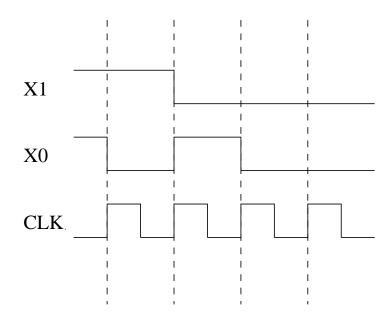

(f) (8 pts) Assume an initial condition of X1 = 1 X0 = 1, and that E = 0. Show the timing diagram for 4 clock cycles (include X1, X0 and CLK).

(g) (5 pts) From the perspective of a Finite State Machine representation of this circuit, what are the events/inputs?

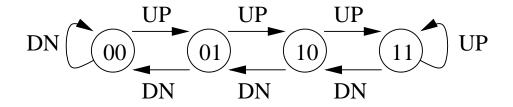

The events are UP (E=1) and DN (E=0), and arrive on the upward transition of the clock.

(h) (10 pts) Show the state transition diagram.

## 2. Arithmetic

Consider the following decimal numbers: X = 38 and Y = 47

(a) (7 pts) What is the two's complement binary representation of -Y (assume an 8 bit representation)?

47 = 00101111so: -47 = 11010001

(b) (8 pts) In binary, subtract Y from X (show your work).

```

38 = 00100110

So:

00100110

+ 11010001

= 11110111

```

(The decimal equivalent of this result is -9.)

### 3. Microprocessor Design

(a) (5 pts) What is the function of the ALU?

The Arithmetic Logical Unit performs (as the name suggests) arithmetic (e.g., add, subtract, multiply, divide) and logical (e.g., and, or, xor) operations on individual or pairs of binary operands

(b) (5 pts) What is the function of the program counter?

The program counter contains the address of the memory location that contains the instruction that is currently being executed.

- (c) (10 pts) Give two examples of signals generated by the instruction decoder.

- Addresses for the registers to be used in the next operation.

- Control signals for the ALU.

- Control and addressing signals for the memory.

- Signals that affect the status register.

- (d) (5 pts) Explain (in brief) the function of the "chip select" signal in a memory circuit.

The chip select signal is used to select an entire memory chip (or module) for a read or write operation. When selected, the state of the module may be altered (in a write operation) or the module may drive the data bus (in a read operation). This type of implementation allows one to have multiple memory modules on the same data bus.

(e) (5 pts) Explain (in brief) the function of the clock signal in a memory circuit.

The clock signal indicates the instant that a write operation is to take place from the data bus into a memory element. Prior to this instant, the memory address must have already been set up.

### 4. Interrupts and I/O

(a) (5 pts) True/false: in pulse-width modulation control, information is encoded in the frequency of the signal.

False. Information is encoded in the duty cycle of the signal.

(b) (7 pts) For the given clock rate and prescaler configuration of the mega8 timer0, give the time (in microseconds) between timer increments (reduced fractions are fine, where necessary).

| Prescaler    | 1 MHz clock  | 16 MHz clock |

|--------------|--------------|--------------|

| No prescaler | $1 \mu s$    | $1/16\mu s$  |

| Div 8        | $8\mu s$     | $1/2\mu s$   |

| Div 64       | $64 \mu s$   | $4\mu s$     |

| Div 256      | $256 \mu s$  | $16 \mu s$   |

| Div 1024     | $1024 \mu s$ | $64 \mu s$   |

(c) (5 pts) Assume that we configure timer0 so that it uses a prescaler of 64 and produces an interrupt. Also assume a clock frequency of 16MHz. How often will an interrupt be generated?

$4\mu s * 256 = 1024\mu s \approx 1ms$

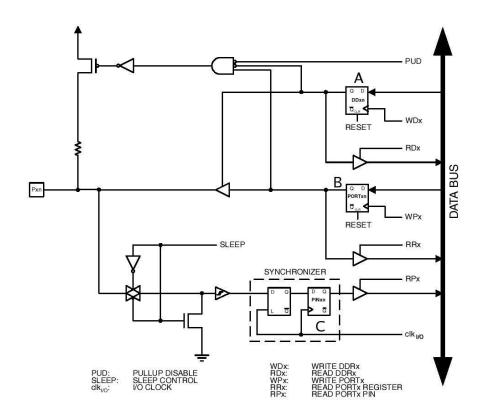

Consider the diagram for PORT B bit 2 (the 3rd bit):

(d) (8 pts) What effect does the following code have on the state of this circuit (in terms of flip-flop state)? What effect does this state change have?

DDRB &= 4;

This one was unintentionally tricky: this does not change the state of flip-flop A (for PB2), but it does set the state of all of the other pins such that they are all inputs.

(e) (8 pts) What effect does the following code have on the state of this circuit (in terms of flip-flop state)? What effect does this state change have?

PORTB &= OxFB;

This operation sets the output state of the pin to 0 (by setting the state of flip-flop B to 0). If this port is configured as an output port, then the pin is set to a low state.

#### 5. Serial Communication

(a) (10 pts) Explain why we do not use a start bit value of "1" in our infrared serial implementation.

In our implementation, a "1" would be encoded with no signal. This choice would mean that the receiver could not distinguish between a start bit and nothing being transmitted. As a result, the receiver would have no timing information with which to synchronize with the transmitter.

(b) (5 pts) Does the receiver or the sender compute the checksum value?

Both sides compute the checksum. (it is the receiver that compares the sent checksum with its own computation of the checksum)

(c) (5 pts) True/False: a UART can perform byte-level error correction and detection.

True

(d) (5 pts) True/False: a UART can perform packet-level error correction and detection.

False. Packet-level communication is application-specific; the UART is focused on application-independent communication.

(e) (5 pts)

Consider a packet that contains the following values: 0x45, 0x12, 0xFA. What is the checksum value?

0x51 (we drop the carry)

## 6. Bonus

What is the magic number?

0xF3

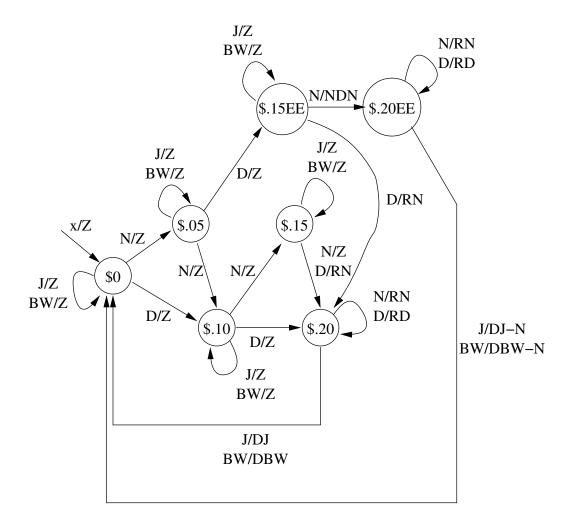

#### 7. Finite State Machines

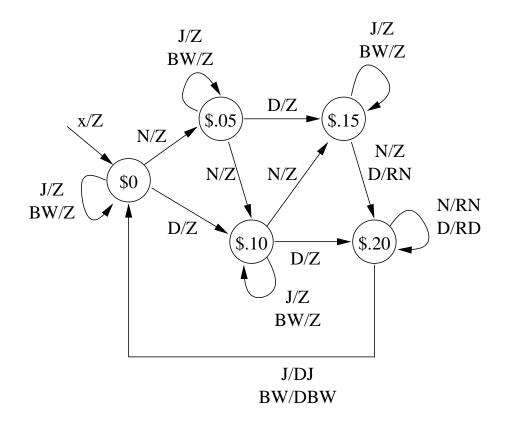

Below is the state transition diagram of the vending machine that we designed in class. Recall that once the machine receives \$.20 (composed of nickels and dimes), it will respond to a button press by dispensing the requested drink (Jolt or Buzz Water). Redesign this FSM to add the following "Easter Egg" feature:

Starting from the \$0 state, if the user inserts the following coins in this specific order: nickel, dime, nickel, the machine immediately returns the three coins and is ready to dispense a drink and an additional nickel.

Where the events are: N = Nickel (insertion); D = Dime (insertion); J = Jolt (request); BW = Buzz Water (request).

And the actions are: RN = Return Nickel; RD = Return Dime; DJ = Dispense Jolt; DBW = Dispense Buzz Water; Z = no action.

Hint: in order to implement the Easter Egg feature, you will need to add additional states and state transitions.

(a) (5 pts) What are the states in this new FSM?

\$0, \$0.05, \$0.15, \$0.15*EE*, \$0.20, and \$0.20*EE* (where "*EE*" stands for Easter *Egg*). We introduced these new states to distinguish between arriving at 20 cents in the special sequence and arriving in any other sequence.

- (b) (5 pts) What are the actions in this new FSM?

- Dispense nickel (RN)

- Dispense dime (RD)

- Dispense Jolt (DJ)

- Dispense Buzz Water (DBW)

- \* Dispense two nickels and a dime (may not be necessary depending on the FSM design). (NDN)

- \* Dispense Jolt and a nickel (same goes for this action). (DJ-RN)

- \* Dispense Buzz Water and a nickel (same). (DBW-RN)

- Nothing (Z)

I will accept the list without the starred items.

(c) (10 pts) Show the state transition diagram (if you choose, you may modify the diagram on the previous page).